由于并聯電抗器在試驗回路中以感性負載呈現��,因此需要在試驗回路中增加大量的容性負載來補償無功�,根據感應電壓試驗要求�,試驗的電壓要達到1.8Ur/√3�,由于并聯電抗器在設計中間隙鐵芯的伏安特性在鐵磁材料飽和與非飽和狀態下存在拐點�,根據法拉第電磁感應原理�,感應電動勢為:

E=4.44fNφ

式中.E——感應電動勢

f——頻率

N一繞組匝數

φ一磁通量

從上式可以看出����,當感應電動勢增加時�,欲保持磁通密度不變��,在匝數一定的情況下��,就必須相應提高試驗頻率����,因此并聯電抗器感應電壓試驗時����,試驗電源的頻率一般為150Hz~200Hz為宜��。

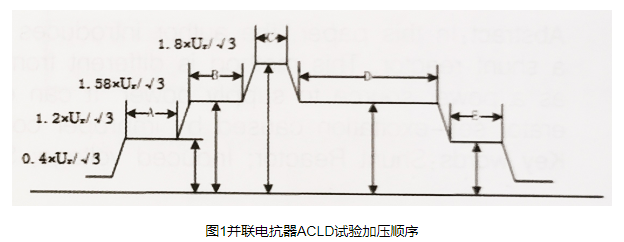

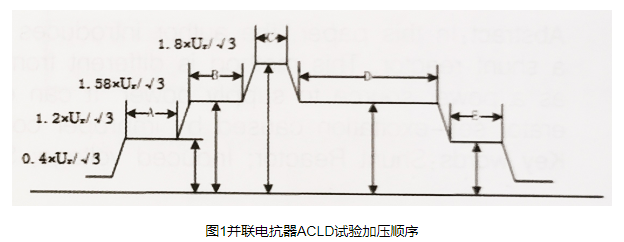

并聯電抗器的感應電壓試驗在高電壓下需要很大的無功功率�,必須要有額定容量足夠的電源���,根據GB1094.3-2018《電力變壓器第3部分:絕緣水平�����、絕緣試驗和外絕緣空氣間隙》中關于帶有局部放電測量的感應電壓試驗(IVPD)的規定�,試驗電壓施加于電抗器繞組兩端���,在不大于0.4×UI/√3的電壓下接通電源��,升高電壓至0.4×UI/√3�,進行背景局放量的測量�,再升至1.2×UI/√3�����,保持至少1分鐘以進行穩定的局放測量����,然后升至測量電壓1.58Ur/√3����,保持至少5min以進行穩定的局放測量��,再升至增強電壓1.8Ur/√3�,保持時間按下述:

(1)當試驗頻率等于或小于2倍額定頻率:Imin�。

(2)當試驗頻率超過兩倍額定電壓頻率時:120×額定頻率/試驗頻率(s)���,不少于15s��。

增強電壓保持之后立刻不間斷地將電壓降至測量電壓保持1h并進行局放量測量���,完畢后���,降低電壓至1.2×UI/√3�����,保持1min并進行穩定的局放測量��,然后降至0.4×UI/√3���,再次進行背景局放量的測量����,最后�,將電壓降至0.4×UI/√3的電壓下����,切斷電源����。

試驗持續時間如圖1所示�。

在施加試驗電壓的1h期間�,每隔5min監測并記錄放電量����,高壓側放電量的連續水平不大于100pC���,且過程中局放水平的增量不大于50pC��。